ОБЗОР ЭЛЕМЕНТНОЙ БАЗЫ АППАРАТНЫХ РЕАЛИЗАЦИЙ НЕЙРОННЫХ СЕТЕЙ

Несмотря на то, что нейронные сети как научно - технический объект существуют более полувека,

основные способы их практической реализации ограничиваются областью программного

моделирования в различных средах визуального и невизуального проектирования.

Программные реализации преобладают над аппаратными.

Кроме того, аппаратные реализации вследствии своей относительной дороговизны до сих пор

не имеют повсеместного распространения. Однако их удельный вес в общем количестве мировых

технологических разработок неуклонно растет. Впереди планеты всей в данном направлении

как всегда шагает Япония, где разработки на основе нейросетевых технологий успешно внедряются

во множестве образцов бытовой техники, таких как фотоаппараты, микроволновки, видеокамеры и т.д.

Не отстают и другие развитые страны.

Нейросетевые аппаратные решения внедряют в свои продукты такие известные фирмы,

как Siemens, Intel, Phillips Research (Нидерланды), 3M Laboratories и многие другие.

При этом разработано на удивление много разнообразных аппаратных нейросетевых архитектур.

Чтобы разобраться в этом зоопарке, наш небольшой обзор нейросетевых реализаций как полагается,

начнем с классификации.

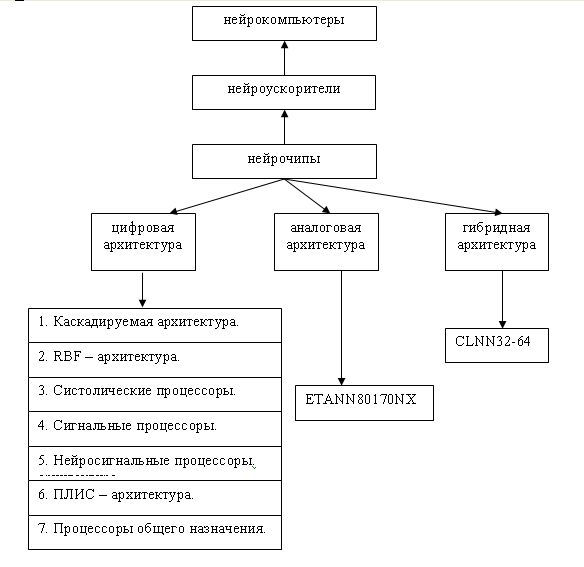

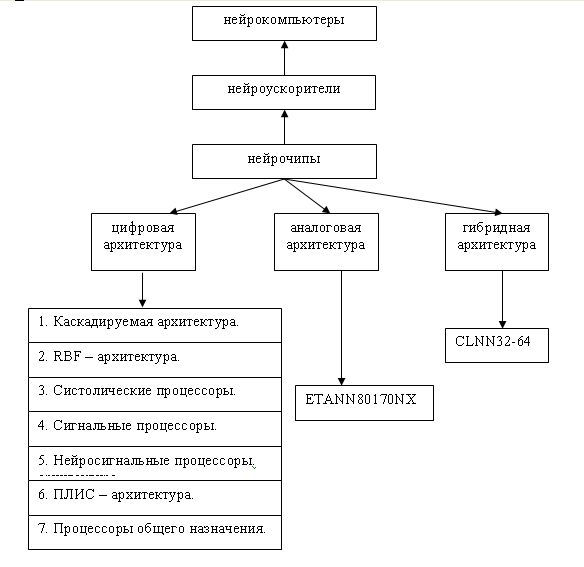

Рис. 1. Классификация нейросетевых архитектур по типу элементной базы.

Теперь рассмотрим отдельные варианты реализации подробнее:

1. Каскадируемая архитектура.

Примером каскадируемой архитектуры может служить нейрочип NNP фирмы Ассurate Automation Corp.

Представляет собой несколько 16 – разрядных процессоров снабженных памятью для хранения весовых

коэффициентов. Процессоры связаны внутренней локальной шиной и имеют всего 9 команд.

В комплект поставки входит библиотека подпрограмм с реализованными нейросетевыми алгоритмами.

Чип выпускается на платах под шины ISA и VME.

Производительность составляет от 140 MCPS до 1,4 GCPS в зависимости от количества нейрочипов на плате.

Их количество может быть от одного до 10.

2. RBF – Архитектура.

Пример – чип Ni1000 (разработка фирмы Intel совместно с Nestor), на котором 3млн. транзисторов,

имитирующих 1024 нейрона, 33 MHz, 17 GIPS. Выпускался на платах в формате ISA, VME.

Кроме того выпускались ныне уже снятые с производства чипы ZICS18T - ZICS24T, которые также представляли

собой нейронные сети на RBF - нейронах.

3. Систолические нейропроцессоры.

Принцип действия систолических процессоров заключается в использовании процессорной матрицы

из набора простых по структуре обрабатывающих элементов, через которую идет непрерывный поток

данных, изменяемых каждым элементом. Сеть работает циклически и в каждом последующем цикле

каждый обрабатывающий элемент считывает и обрабатывает новую порцию данных, независимо от

работы остальных обрабатывающих элементов. За счет этого достигается высокая степень распараллеливания

процессов обработки информации и высокая скорость работы всей сети в целом.

Вследствие значительного упрощения внутренней структуры обрабатывающих элементов, систолическая

матрица должна быть окружена большим количеством элементов, реализующих дополнительную

функциональность. Например, функция активации должна быть реализована в виде отдельного внешнего блока.

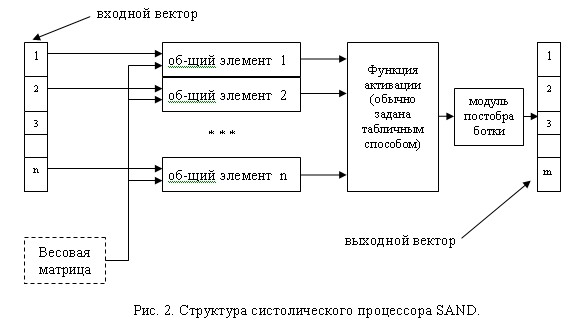

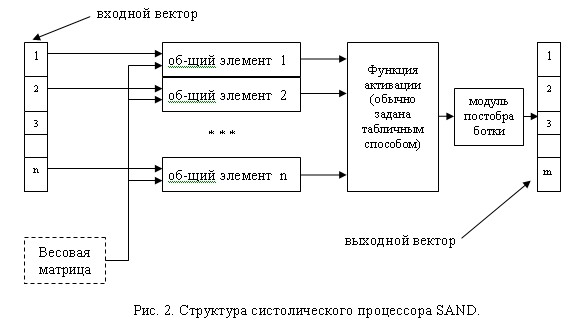

На рис 2 показана структурная схема систолического процессора SAND (Simple Applicable Neural Device).

Чип разработан разработан Исследовательским центром в Карлсруе и Институтом микроэлектроники Штутгарта.

В состав периферийных устройств входит также модуль постобработки и модуль памяти весов.

Обрабатывающие элементы выполняют операции перемножения входных сигналов и суммации их.

Все остальные операции реализуются внешними логическими блоками.

В некоторых случаях в качестве внешнего блока может использоваться блок вычисления минимума или

максимума выходного значения.

Сравнительно низкая стоимость разработки, обширная элементная база с обилием отладочных

средств и вспомогательного софта, экономичное энергопотребление и малое тепловыделение,

а также высокая производительность сделали сигнальные процессоры фирм Texas Instruments и

Analog Devices наиболее популярными объектами для построения аппаратных реализаций нейронных сетей.

Моделирование нейронных сетей на сигнальных процессорах осуществляется только программным

способом, что позволяет в случае необходимости легко модифицировать используемый алгоритм

и структуру сети.

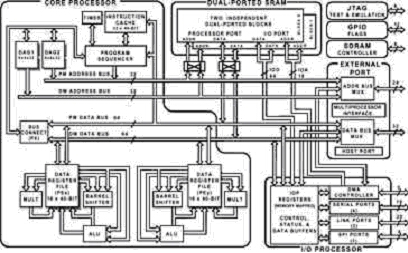

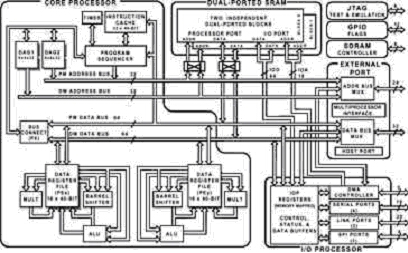

Например, использование разработчиками DSP серии ADSP2106x компании Analog Devices оправдывается

рядом удачных конструктивных решений, заложенных в архитектуру этих чипов. ADSP2106x используют

архитектуру SHARC (Super Harvard ARChitecture), которая предполагает разделение памяти и шин команд

и данных, при этом по шине команд могут передаваться как команды, так и данные.

Процессор имеет два генератора адреса данных, что позволяет одновременно генерировать два адреса

для выборки двух операндов.

Объем внутренней памяти 1 Мбит позволяет реализовать достаточно крупные нейронные сети.

Система команд ADSP2106x содержит арифметическую команду умножения с накоплением C=A*B+C,

что достаточно удобно для построения циклов вычисления входных значений нейронов.

Микропроцессор использует циклические буферы при обращении к которым происходит

автоматическая модификация адресов, что позволяет упростить циклы и увеличить скорость

работы сети. Кроме того ADSP2106x использует два вычислительных блока (обрабатывающих элемента,

PEx и PEy) вместо одного.

В стандартном режиме используется только PEx. В режиме SIMD (Single Instruction, Multiple Data)

процессор направляет одну и ту же инструкцию в оба процессорных элемента, загружает два отдельных

набора данных из памяти в каждый PE, производит параллельные вычисления в обоих PE и

синхронизирует результаты в памяти. Таким образом, использование двух параллельно работающих

процессорных элементов позволяет в два раза увеличить скорость обработки данных, что весьма

актуально при моделировании нейронных сетей, состоящих из множества однотипных элементов.

В основе нейросигнальных процессоров лежит то же самое ядро, что и для других распространенных

процессоров DSP. Отличие заключается в добавочных архитектурных решениях,

оптимизирующих данные процессоры для разработок на их базе нейронных сетей.

В качестве примера приведем наш отечественный нейропроцессор NEUROMATRIX NM6403 фирмы «Модуль».

Данный процессор состоит из основного 32 – разрядного RISC ядра, и добавочного 64 –

разрядного векторного сопроцессора. NM6403 имеет стандартный интерфейс ввода - вывода,

совместимый с портами TMS320C4, может работать с числами переменной разрядности от 1 до 64 бит,

адресное пространство – до 16 Гбайт, поддержку векторно – матричных и матрично – матричных операций,

поддержку двух типов функций насыщения на кристалле. Его производительность по скалярным

операциям составляет 120 MOPS (32 – разрядные операнды) и от 40 до 11500 ММАС

(миллионов умножений с накоплением в секунду). Желающие могут более подробно ознакомиться

с документацией и всеми спецификациями этого процессора на сайте разработчика [3].

Здесь в заключение отметим, что хотя процессор NM6403 за счет оригинальной архитектуры

значительно лучше справляется с матричными операциями, чем другие DSP, однако вся тяжесть

программной реализации выбранной нейронной сети по-прежнему лежит на разработчике.

6. ПЛИС как элементная база нейронных сетей.

В последние годы резко возрос интерес к использованию ПЛИС в качестве элементной базы нейровычислителей.

Этому способствовало появление на рынке высокочастотных ПЛИС и продолжающаяся тенденция к снижению их цены,

а следовательно и конечной стоимости разработок. Напряжение питания ПЛИС с каждым новым поколением

этих микросхем постоянно уменьшается, что позволяет снижать энергопотребление при увеличенном быстродействии.

Современные ПЛИС изготавливаются такими известными производителями как Altera, Atmel, Xilinx и многими другими.

Технологические особенности FPGA ПЛИС делают их удобным объектом для использования в качестве элементной

базы аппаратной реализации нейронных сетей. К ним относятся необходимость восстановления структуры

устройства с помощью внутреннего статического ОЗУ, что позволяет реализовать алгоритмы обучения нейронной сети.

При разработке проектов на ПЛИС используется принцип однотактной синхронизации, для реализации которого

в ПЛИС синхросигналы распространяются по быстродействующей древовидной сети, обеспечивающей почти

одновременный приход фронта синхроимпульса на синхровходы всех внутренних триггеров.

Синхросигнал может вырабатываться и внутри самой ПЛИС.

Данное свойство позволяет облегчить задачу построения многослойных конфигураций нейронных сетей.

Современные ПЛИС практически невозможно программировать вручную. Для разработки проектов исполь

зуются специальные среды программирования и языки параллельного программирования (VHDL) [4].

Это позволяет снять зависимость разработок нейронных сетей на ПЛИС от конструктивных особенностей

конкретной ПЛИС, улучшить переносимость, а также создавать библиотеки стандартных нейросетевых модулей,

что выгодно отличает нейросетевые проекты на ПЛИС от аналогичных разработок на DSP.

Наконец, ещё одной немаловажной особенностью ПЛИС, делающей привлекательными разработки нейронных

сетей на этой элементной базе является то обстоятельство, что любая ПЛИС состоит из множества однотипных

элементов, что повышает надежность работы микросхемы и упрощает проектирование нейронной сети.

Вместе с тем для проектирования нейронных сетей на ПЛИС характерны достаточно высокие аппаратные затраты.

Если учесть, что для реализации десятка параллельно работающих нейронов требуется задействовать несколько

тысяч вентилей, и при этом каждый нейрон требует как минимум одного умножителя, можно сделать вывод,

что существующие на сегодняшний день на рынке ПЛИС с интеграцией в несколько миллионов вентилей наиболее

пригодны для реализации малых и средних по величине нейронных сетей порядка нескольких тысяч

нейронов и не пригодны для создания больших и сверхбольших нейронных сетей, содержащих сотни тысяч

или миллионы нейронов.

Примером реализации нейронной сети на ПЛИС может служить нейромодуль цифровой обработки

сигналов XDSP – 680 – CP фирмы СканИнжиниринг Телеком.

7. Процессоры общего назначения.

Подавляющее большинство нейросетевых реализаций в настоящее время осуществляется на базе процессоров

общего назначения. Этому способствует широкое распространение персональных компьютеров и

впечатляющий рост их производительности. На данный момент создана масса программ и

программных библиотек, эмулирующих нейронные сети различных конфигураций.

Однако данные нейросетевые реализации осуществляются исключительно на программном уровне,

поэтому в данном обзоре рассматриваться не будут.

8. Выбор элементной базы для аппаратной реализации нейронных сетей.

Несмотря на то, что в настоящее время большинство нейросетевых приложений выпускаются

исключительно в программном исполнении с использованием коммерческих программных

эмуляторов нейронных сетей, существует достаточно широкая рыночная ниша для нейрочипов

или нейросетевых аппаратно – программных комплексов.

Наиболее весомые аргументы в пользу применения специализированного аппаратного обеспечения

возникают в следующих случаях:

- если сложность решаемой задачи достаточно велика, и нейросетевые реализации не обеспечивают

должную скорость выполнения или производительность (например, эксперименты в области физики высоких энергий).

- если стоимость проектирования специализированной аппаратной нейросетевой системы на

готовых нейросетевых модулях значительно ниже, чем её программного аналога.

- если требуется обеспечить решение задачи, алгоритм которой заведомо допускает массовое

распараллеливание, и система будет эксплуатироваться в полевых условиях, что предъявляет

повышенные требования к её надежности (например, система сбора и обработки данных погодных датчиков на аэродроме).

- если имеются существенные ограничения на габариты системы, или её вес.

- если предъявляются повышенные требования к безопасности системы, поскольку аппаратные

решения больше защищены от несанкционированного доступа и обеспечивают большую

защиту авторских прав на схемотехнические и архитектурные решения.

Исходя из опыта практической деятельности современного инженера – электронщика следует заметить,

что при проектировании аппаратной реализации нейросистем учитываются прежде всего такие

характеристики как масштабируемость, стоимость разработки, совместимость с предыдущими и будущими версиями.

Применительно к рассмотренным категориям чипов это означает, что в случае, когда для разработчика

критичны сроки разработки и стоимость, следует обратить внимание на ПЛИС,

сигнальные процессоры и процессоры для каскадируемых архитектур. ПЛИС способны неплохо

масштабироваться и достаточно дешевы, но затраты аппаратных ресурсов ПЛИС при проектировании

достаточно велики и быстро растут с увеличением сложности сети.

Сигнальные процессоры масштабируются хуже чем ПЛИС, но разработка нейронных сетей на них

благодаря развитой технической поддержке со стороны производителей достаточно проста.

При этом привязка к аппаратной части DSP не позволит с легкостью переносить нейронную сеть

с одной элементной базы на другую. Кроме того сигнальные процессоры обладают не слишком

хорошей масштабируемостью, что затрудняет построение больших многопроцессорных систем.

Систолические процессоры и процессоры с каскадной архитектурой обладают на порядок лучшей

масштабируемостью, чем сигнальные, однако для них требуется достаточно много периферийных модулей.

С увеличением числа систолических процессоров, растут задержки в цепях прохождения сигнала.

Для нейросигнальных процессоров в целом характерно всё то же самое, что справедливо для

сигнальных процессоров. Отличия заключаются в более высокой производительности за счет

наличия встроенного векторного сопроцессора, и более узкой специализации в большинстве

случаев ориентированной на конкретный вид нейронной сети. Таким образом общепринятых

рекомендаций по выбору определенной элементной базы в настоящее время не существует.

Всё это в значительной степени определяется личным опытом разработчика, его предпочтениями,

а также доступностью на данной территории тех или иных электронных компонентов.

ЛИТЕРАТУРА

1. http://chipnews.gaw.ru/html.cgi/arhiv/00_07/stat_36.htm - описание, таблица сравнительных характеристик элементной базы современных нейрочипов.

2. http://www.module.ru/ruproducts/proc/nm6403.shtml#descr

3. Сергиенко А.М. VHDL для проектирования вычислительных устройств. - Киев.: ЧП «корнейчук», ООО «ТИД ДС», 2003. – 208 с.

Комментарии пользователей:

| Flora | 2016-10-21 23:48:42 |

| An inelteiglnt point of view, well expressed! Thanks! |